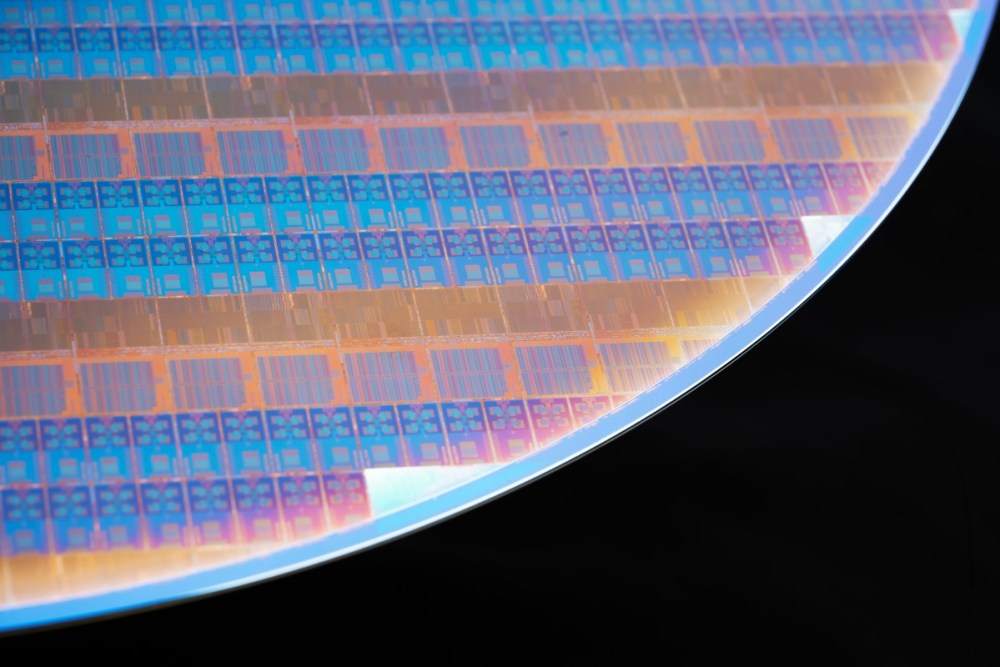

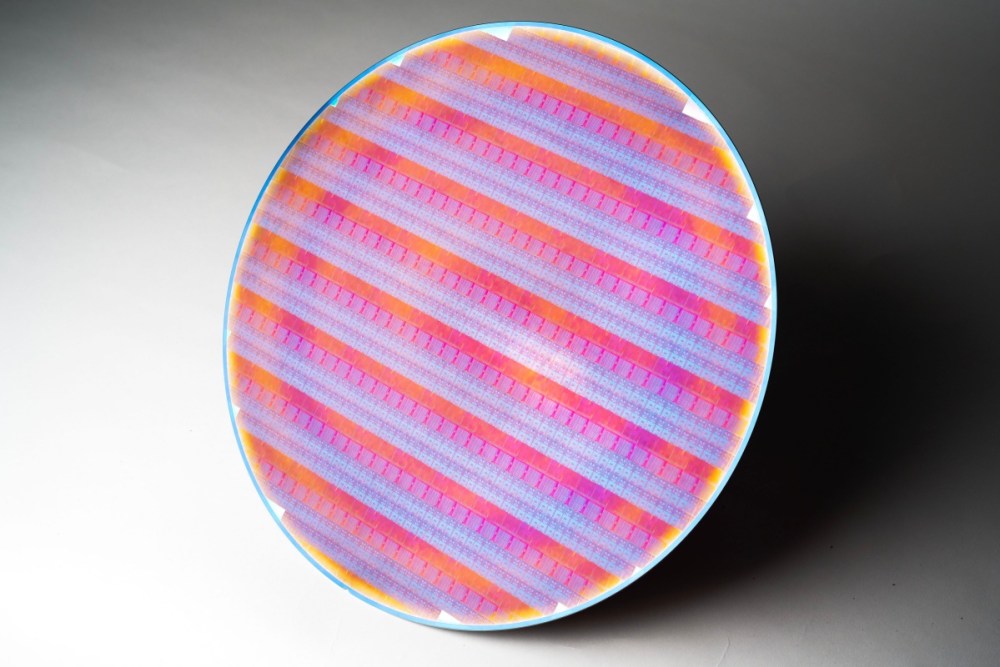

先前说明将用于Intel 20A (埃米)制程的RibbonFET晶体管技术与PowerVia供电设计,Intel稍早说明在类产品测试芯片实作中,PowerVia供电设计实现超过90%的单元利用率。

PowerVia供电设计是将电源回路移到晶圆背面,藉此解决芯片面积持续微缩情况下的电路连接瓶颈,而此次测试更实现超过90%的单元利用率,让芯片设计人员能够在产品中提升效能和效率。

而此次测试更利用EUV (极紫外光)微影设计规则,并且在芯片面积上达成超过90%的标准单元利用率,藉此提高单元密度,同时也降低成本。 同时,此测试更凸显平台电压下降幅度超过30%,以及6%的频率优势。

另外,Intel也将针对逻辑单元微缩伴随的高功率密度,在PowerVia测试芯片达成所需散热效果。

Intel预计在2024年将PowerVia与RibbonFET环绕式栅极(gate-all-around)技术用于芯片产品,分别用于Intel 20A和Intel 18A制程技术。

还木有评论哦,快来抢沙发吧~